XILINX 社の FPGA Spartan-3A 評価キットでプログラムを書いてボード上で実行するまでの最低限の手順を書きます。特に英語版を買った人は、箱に入っている資料では全く役に立たないので注意して下さい。でも XILINX のサイトに沢山情報があります。

ソフトウェアのインストール

付属の CD-ROM から ISE 9.2i 評価版をインストールしました。インストール時に XILINX ウェブサイトでキーを発行してもらう必要があります。EDK は不要です。

FPGA の動作原理

普通 IC というのは作ってから中の回路を変更する事が出来ません。しかし FPGA には回路の素が沢山入っていて、ビットストリームという情報から動的に回路を作り出します。つまり後から CPU にもメモリにも何にでもなる、チップ界の ES 細胞と言えます。残念ながら回路の合成は電子的に行われるので、回路の素がうようよ動いて結合してゆくわけではありません。また、デジタル回路しか出来ないので FPGA でラジオやアンプは作れません。

パソコンからビットストリームを FPGA にダウンロードすると、すぐさま FPGA は新しい回路として動き始めます。ダウンロードと言うのはデータをデバイスに書く時に使う用語なので注意してください。電気を消すとビットストリームも消えるので、普通は PROM に書き込み起動時に毎回ロードします。評価キットには PROM も付いています。開発の手順は以下の通りです。

ISE を起動する。

スタート - Xilinx ISE 9.2i - Project Navigator で起動します。ISE というのは、FPGA 開発に使われるいくつかのツールを纏めて実行出来るようにした物です。他のツールを呼び出す際にウイルスチェッカーが警告を出す場合があるので注意してください。

新規プロジェクトを作成

- File - New Project

- New Project - Wizard Create New Project

- Project Name : bit

- Project Location : 適当に

- New Project - Device Properties

- New Project - Create New Source

- New Source Wizard - Select Source Type

- Verilog Module を選択

- File name : bit

- New Source Wizard - Define Module 無視してそのまま Next

- New Source Wizard - Select Source Type

- のこりそのまま Next や Finish

- Source タブ - チップのアイコンを展開して bit.v を右クリック

- New Source

- Implementation Constraints File を選択

- File Name : bit

- Process タブ - User Constraints - Edit Constraints (Text) ダブルクリック

ソースコードを書く。

画面に空っぽのテキストファイルが二つ出てくるので、内容を書きます。

bit.v : 回路を記述する Verilog HDL ファイルです。たんにスイッチと LED を繋ぐだけのしょうもない回路です。

`timescale 1ns / 1ps module bit(switch, led); input switch; output led; assign led = switch; endmodule

bit.ucf : ピンの位置やタイミングを決めるファイルです。NET 変数名 LOC = ピン位置; のように書くみたいです。ピン位置はユーザーガイドに書いてあります。PULLDOWN というのは、何だかよく分かりませんが無いと不安定なので付けてみました。

NET "led" LOC = "R20"; NET "switch" LOC = "T15" | PULLDOWN ;

Process タブ - User Constraints - Assign Package Pins をダブルクリックして GUI でピンを決める事も出来ます。

ボードにダウンロードしてちゃんと動くか確認。

まずケーブルを繋いで、ドライバをインストールします。

- USB ケーブルを繋ぐ

- ボードの電源を入れる

- デバイスに必要なファイルは C:\Xilinx92i\bin\nt\xusb_emb.sys にある。

ちゃんと繋げたらいよいよ実験

- Source タブに戻り bit.v が選択されている事を確認

- Process タブ Generate Programing File

- Configure Device (iMPACT) ダブルクリック

- iMPACT Welcome to iMpact

- Configure devices using Boundary-Scan (JTAG) を選択

- Assign New Configuration File

- File name : bit.bit

- Warning 'JtagClk' が変わったと言われるがそのまま OK

- Assing New Configuration File

- mcs ファイルはまだ無いので Cancel

- チップの絵が出るので、xc3s700a を右クリック - Program...

- Verify をチェックしないでそのまま OK

これで、ボードの SOUTH ボタンを押すと LED0 が光るという凄い回路が完成しました!

PROM 用のファイルを作る

このままでは電気を切ると回路を忘れてしまうので、PROM に保存します。PROM ファイルを作るのも ISE でそのまま出来るはずですが、何故か上手く行かないので iMPACT を直接起動します。

- スタート - Xilinx ISE 9.2i - アクセサリ - iMPACT

- create a new project を選択

- Welcome to iMPACT

- Prepare a PROM File を選択

- Prepare PROM Files

- I want to target a : Xilinx PROM

- PROM File Format : MCS

- PROM File Name : bit

- Specify Xilinx PROM Device

- Auto Select PROM

- File Generation Summary -> Finish

- Add Device : bit.bit を選択

- Add Device : No

- Operations - Generate File...

これで PROM ファイルが出来ました。

PROM ファイルを転送

- ISE に戻る

- Boundary Scan タブ

- xcf04s (右側のチップ)をダブルクリック

- 先ほど作った bit.mcs を選択

- xcf04s を右クリック - Program ... で書き込み

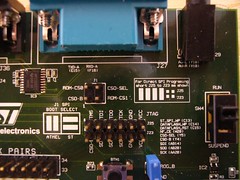

さて、これからが問題。このスターターキットはオマケとして沢山色んなメモリが付いていて、買ったばかりの時は AMTEL という Flash メモリから回路を読むようになっています。先ほどの操作で書き込んだのは内臓 PROM なので、ちゃんとここから起動するようにジャンバで設定します。PROM です。

元の状態

- J1 縦二列(AMTEL)

- J46 なし

内臓 PROM (プラットフォーム PROM) にするには

- 電源を切る

- J1 なし

- J46 CE PROM と GND を繋ぐ(DONE でも良い。ユーザーガイド参照)

これで電源を切っても大丈夫です。完成!

おまけ。回路の確認。

実際にどのように配線されるのか見たり編集する事も出来ます。

- Process タブ - Implement Design - Place & Route - View/Edit Routed Design (FPGA Editor)

- List Window で All Nets を選択

- 配線が表示されるのでズームしてしみじみ眺める

感想

付属ドキュメントのあまりの不備さにびっくりしました。折角買っても訳の分からない人が沢山いると思います(そういう人は買わないのかな)。特に、EDK に惑わされました。今回操作の仕方を書きたかったのでプログラムに凝りませんでした。

FPGA のコンセプトだけ体験したい人には、Spartan-3 は高級すぎるかも知れません。電子工作にちょっと組み込む物では無いです。CPLD というもっと手軽なやつもあるみたい。私がこれを選んだのは画像処理チップやシンセサイザを作ってみたかったからだけど道は遠いです。

資料

- ここから沢山資料を探せます。

- スパルタン3スタータキットでのISE8.1iのチュートリアル8(コンフィギュレーション編続き)

- Spartan-3A スタータキット